GPIO

General-Purpose Input/Output (GPIO) pins can be configured as either inputs or outputs. Many signals on the phyCORE-Connector can be used as GPIOs through multiplexing. The AM64x processor features five independent GPIO modules. For detailed information about the phyCORE-AM64x GPIO interface, please refer to the GPIO section in the Hardware Manual

GPIO Signal Names and Chip Mapping

GPIOn_x is a generic name used to describe a GPIO signal, where n represents the specific GPIO module and x represents one of the input/output signals associated with the module. Usually you find these names in the schematics and in comments in our device trees in the muxing section.

The AM64x provides three GPIO modules:

GPIO0

GPIO1

MCU_GPIO0

Linux represents these modules as gpiochips. You can list them using the gpiodetect command:

sh-phyboard-electra-am64xx-2:~# gpiodetect

gpiochip0 [4201000.gpio] (23 lines)

gpiochip1 [600000.gpio] (87 lines)

gpiochip2 [601000.gpio] (88 lines)

The second column shows the hardware address of each GPIO module. In the device tree, these GPIOs are accessed using node labels:

main_gpio0 (gpio@600000)

main_gpio1 (gpio@601000)

mcu_gpio0 (gpio@4201000)

Note

GPIO chip numbers may change between system boots. For consistent numbering, configure udev rules.

Active GPIO Signals

The following command shows GPIO signals that are currently allocated by kernel drivers. These GPIOs are already in use and attempting to access them with gpioget or gpioset will result in a “Device or resource busy” error.

See the allocated GPIO signals by running:

sh-phyboard-electra-am64xx-2:~# cat /sys/kernel/debug/gpio

gpiochip0: GPIOs 512-534, parent: platform/4201000.gpio, 4201000.gpio:

gpiochip1: GPIOs 535-621, parent: platform/600000.gpio, 600000.gpio:

gpio-547 ( |green:heartbeat ) out lo

gpio-550 ( |red:disk ) out lo

gpio-551 ( |green:disk ) out lo

gpio-552 ( |home ) in lo

gpio-556 ( |menu ) in lo

gpio-567 ( |standby ) out lo

gpio-570 ( |standby ) out lo

gpio-598 ( |PHY reset ) out lo ACTIVE LOW

gpiochip2: GPIOs 622-709, parent: platform/601000.gpio, 601000.gpio:

gpio-640 ( |PHY reset ) out lo ACTIVE LOW

gpio-641 ( |PHY reset ) out lo ACTIVE LOW

gpio-665 ( |spi1 CS1 ) out lo ACTIVE LOW

Using GPIOs

To access GPIOs from userspace applications, use the libgpiod library. This library provides tools for interacting with Linux GPIO devices. Here are some common usage examples:

List all available GPIO chips:

sh-phyboard-electra-am64xx-2:~# gpiodetect

gpiochip0 [4201000.gpio] (23 lines)

gpiochip1 [600000.gpio] (87 lines)

gpiochip2 [601000.gpio] (88 lines)

Display detailed GPIO chip information (names, consumers, direction, active state, and flags):

sh-phyboard-electra-am64xx-2:~# gpioinfo -c gpiochip2

Read the value of a GPIO (e.g GPIO 36 from chip2):

sh-phyboard-electra-am64xx-2:~# gpioget -c gpiochip2 36

Set the value of GPIO 36 on chip2 to 0 and exit tool:

sh-phyboard-electra-am64xx-2:~# gpioset -z -c gpiochip2 36=0

Note

Interacting with a Signal as GPIO requires a proper muxing. The signal needs to be muxed in mux mode 7 (GPIO).

GPIOs via sysfs

Warning

Accessing GPIOs via sysfs is deprecated. We strongly encourage using libgpiod instead.

Sysfs GPIO access is no longer enabled by default. To enable it, enable CONFIG_EXPERT & CONFIG_GPIO_SYSFS in the kernel configuration.

Using LEDs

The phyBOARD-Electra AM64x features several user-controllable LEDs that are connected to GPIO pins. While these LEDs can be controlled through the standard GPIO interface, Linux provides a dedicated LED subsystem that offers a more convenient way to manage them.

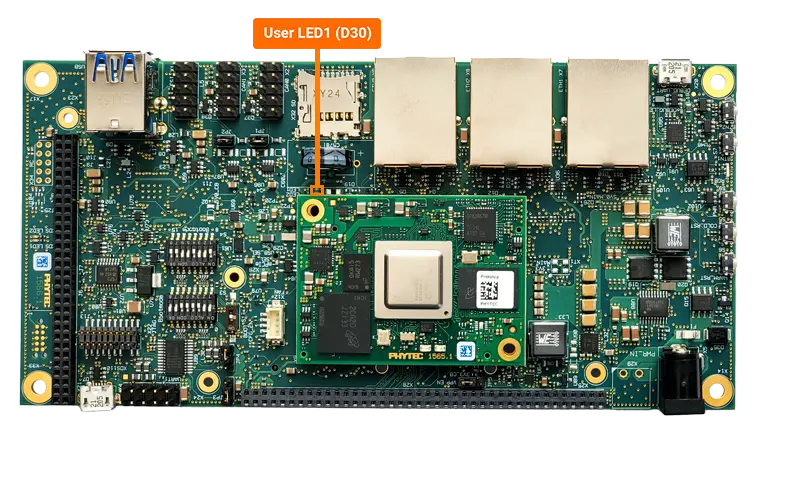

Location of user LEDs:

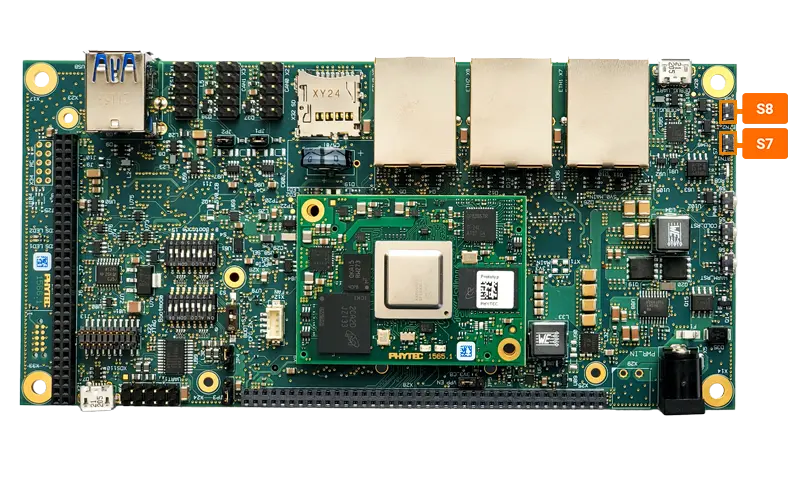

Location of user Buttons:

LED Control Interface

The LED subsystem is accessible through the sysfs interface at /sys/class/leds/. Each LED has its own directory containing control files:

brightness: Write values to control the LED state0turns the LED offAny non-zero value turns the LED on

max_brightness: Read-only file showing the maximum brightness valuetrigger: Allows setting automatic triggers (e.g., heartbeat, disk activity)

Note

While the interface supports brightness levels, most onboard LEDs are simple on/off LEDs without hardware brightness control. Any non-zero brightness value will simply turn them on.

Available LEDs

To list all available LEDs on your system:

sh-phyboard-electra-am64xx-2:~# ls /sys/class/leds/

blue:user@ green:disk@ green:heartbeat@ green:user@ mmc0::@ mmc1::@ red:disk@ red:user@

Controlling LEDs

You can control LEDs using simple shell commands:

To toggle the LEDs ON:

sh-phyboard-electra-am64xx-2:~# echo 255 > /sys/class/leds/red\:user/brightness

To toggle the LEDs OFF:

sh-phyboard-electra-am64xx-2:~# echo 0 > /sys/class/leds/red\:user/brightness

Advanced Usage

For more details about LED configuration, refer to the Linux kernel documentation at https://www.kernel.org/doc/Documentation/leds/leds-class.txt

Set LED triggers (e.g., for heartbeat effect):

sh-phyboard-electra-am64xx-2:~# echo heartbeat > /sys/class/leds/green\:heartbeat/trigger

Disable LED trigger:

sh-phyboard-electra-am64xx-2:~# echo none > /sys/class/leds/green\:heartbeat/trigger