Boot without Pressing the Power Button

The phyCORE-i.MX7 System on Module by default requires a power button to be pressed in order to boot the device. This application note will explain the default behavior in depth and provide a solution for changing the behavior of the SOM so that a button press is not required to boot the device.

Default Behavior

The i.MX7 Processor supports various power modes including:

OFF Mode

Secure Non-Volatile Storage (SNVS) Mode

Low Power State Retention (LPSR) Mode

RUN Mode

Low Power Mode

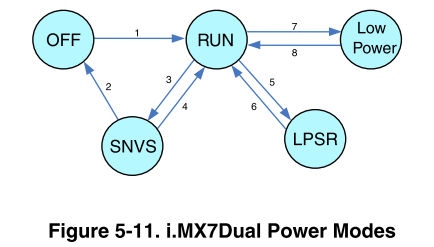

This application note will focus on ‘OFF’, ‘RUN’, and ‘SNVS’ mode. The below snapshot (Figure 5-11 and Table 13) was taken from NXP’s i.MX7Dual Applications Processor Reference Manual, Rev. 0.1, 08-2016. Please refer to this manual for additional details on the available modes.

In addition to ‘RUN’ and ‘OFF’ modes, the phyCORE-i.MX7 SOM has been designed to support the low power Secure Non-Volatile Storage (SNVS) mode. When in this mode, a portion of the i.MX7 chip is in a low power state where only RTC and tamper detection logic is active.

SNVS mode requires VDD_SNVS_IN to be present. The phyCORE-i.MX7 SOM is configured such that the VDD_SNVS_IN rail is always supplied. When power is applied, VDD_SNVS_IN is sourced from ‘VIN’ (tied to VCC_SOM). Likewise, when power is removed, VDD_SNVS_IN is sourced from a ‘LICELL’ coin cell supply (tied to VBAT) via the 0 ohm resistor R172 on the SOM. As long as there is a valid voltage present from either power applied or there is a charged battery attached, the i.MX7 processor will not transition from ‘RUN’ to ‘OFF’ mode. Instead it will transition from ‘RUN’ to ‘SNVS’ mode. The transition from ‘RUN’ to ‘SNVS’ (step 3 in the above Figure) can be triggered by the following:

Software controlled power off - For example, safe shut down of the system using the ‘poweroff’ command in Linux.

Long ONOFF signal press - phyCORE-i.MX7 SOM signal X_MX7_ONOFF is connected to a button on the phyBOARD-Zeta. If this button is held it will trigger a move between power states.

To then boot the board and bring the i.MX7 from ‘SNVS’ to ‘RUN’, this can be triggered by the following actions:

ONOFF signal press - The phyCORE-i.MX7 SOM’s X_MX7_ONOFF signal is connected to a Power button on the phyBOARD-Zeta. This button must be pressed to boot the board.

RTC event

Tamper event

Due to VDD_SNVS_IN always being present, a button press will always be required to boot the system after power is first connected.

Note

The button press may not be required if the Coin Cell battery is allowed to discharge completely.

Power On Without a Button Press

If your use case requires the board to boot up without a button press, the VDD_SNVS_IN supply will need to be removed to transition the i.MX7 from ‘RUN’ mode to ‘OFF’ mode, bypassing ‘SNVS’ mode. Currently when power is removed, VDD_SNVS_IN is sourced from ‘LICELL’ coin cell supply (tied to VBAT). As long as there is a charged battery supplying the VBAT rail, VDD_SNVS_IN will be supplied and the board will remain in ‘SNVS’ mode. One solution is to not supply VDD_SNVS_IN when power is cut from the system. This can be done by removing the connection between VBAT and the i.MX7.

Please note that this solution will require the SOM to be power cycled in order to boot the device (which forces an automatic ‘OFF’ to ‘RUN’ transition). If you are using software or an ONOFF long press to turn off the phyCORE-i.MX7 and VCC_SOM is still supplied, the board will still transition into the ‘SNVS’ mode until the VCC_SOM supply is removed. In that case, a button press or RTC/tamper event will be required to transition into ‘RUN’ mode from ‘SNVS’.

Below are a couple options to disconnect VBAT from the i.MX7 processor:

Do not supply the VBAT rail on your carrier board design.

Note

Discrete RTC functionality will be lost.

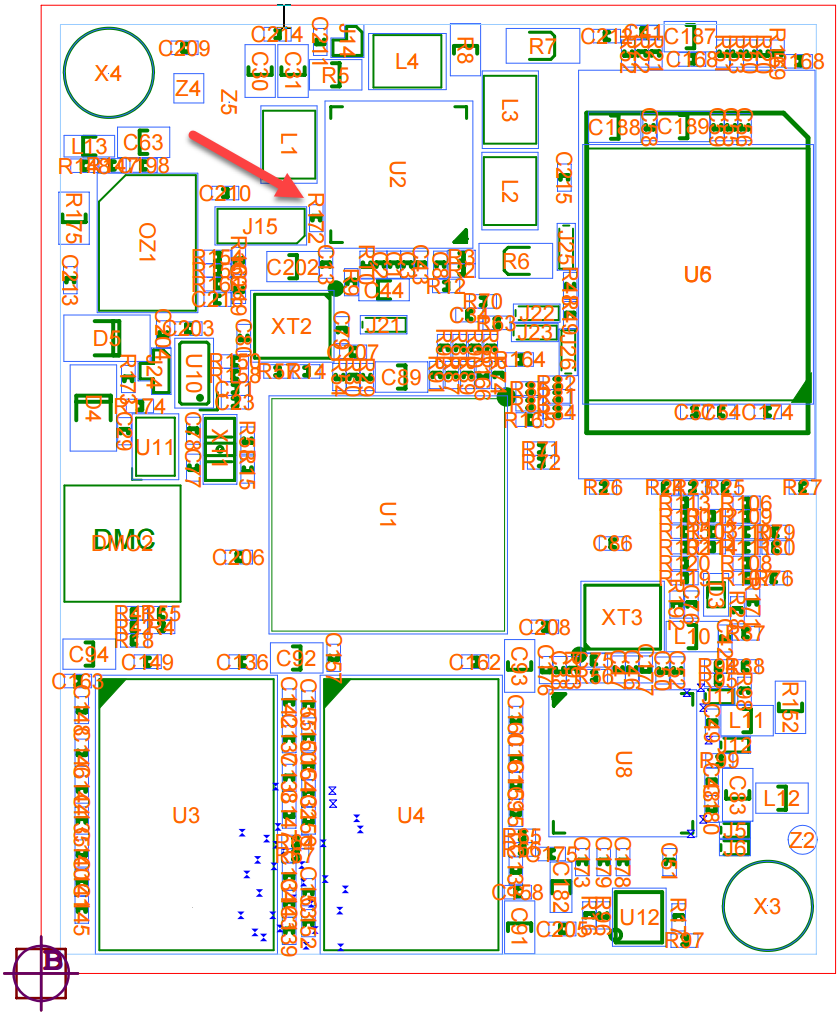

Depopulate R172 on the phyCORE-i.MX7 SOM. This will disconnect VBAT from the LICELL pin, while still allowing it to supply the discrete RTC.

Note

If you find that your final production design requires the R172 resistor to be removed from the SOM and you are beginning to think about placing a large SOM order with PHYTEC, be sure to contact support@phytec.com to help you get setup with a custom SOM configuration where the R172 resistor is left out by default for you.